PSPICE Netlist

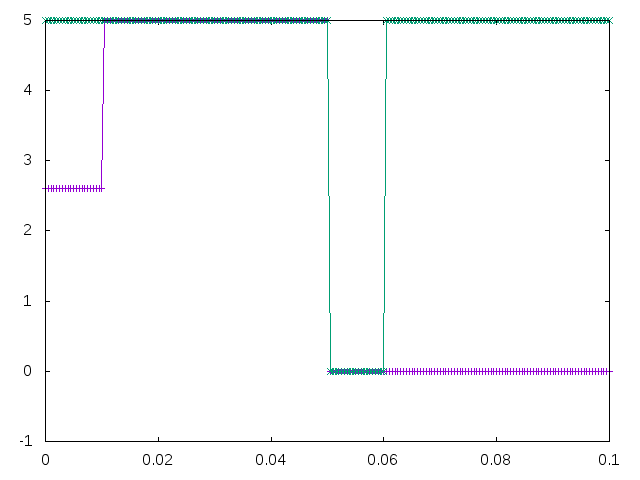

*RS Flip-Flop VCC 5 0 5V VI1 1 0 PWL(0ms 5 10ms 5 10.01ms 0 20ms 0 20.01ms 5 ) VI2 2 0 PWL(0ms 5 50ms 5 50.01ms 0 60ms 0 60.01ms 5 ) XNAND1 1 4 3 5 0 NAND XNAND2 2 3 4 5 0 NAND .SUBCKT NAND 1 2 3 5 6 M1 3 1 5 5 PMOS1 M2 3 2 5 5 PMOS1 M3 3 1 4 4 NMOS1 M4 4 2 6 6 NMOS1 C1 3 6 0.01p .ENDS .MODEL NMOS1 NMOS .MODEL PMOS1 PMOS .OP .TRAN 0.5ms 100ms .PLOT TRAN v(3) v(2) v(1) .END .

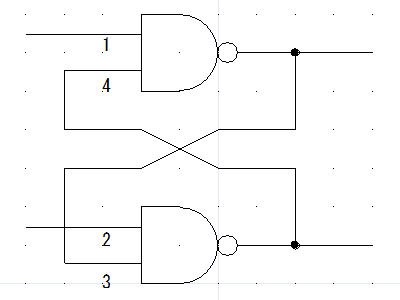

CMOS RS FlipFlop Fig.( spice_CMOS-RSFlipFlop_FIG.DXF )

CMOS RS FlipFlop PSPICE Netlist( spice_CMOS-RSFlipFlop.txt )